# Eight-Channel, High Speed, ±60V, ±1.0A, Ultrasound RTZ Pulser

#### **Features**

- ► HVCMOS technology for high performance

- ► High density integrated ultrasound transmitter

- 0 to ±60V output voltage

- ▶ ±1.0A source and sink current in pulse mode

- ▶ ±1.0A source and sink current in RTZ mode

- Up to 20MHz operating frequency

- Matched delay times

- Optional clock re-alignment

- 3.3V CMOS logic interface and reference

- +3.3V low voltage supply for V<sub>DD</sub>

- Built-in linear regulators for floating gate driver

- Built-in output drain diodes & bleed resistors

### **Application**

- Portable medical ultrasound imaging

- Piezoelectric transducer drivers

- Pulse waveform generator

### **General Description**

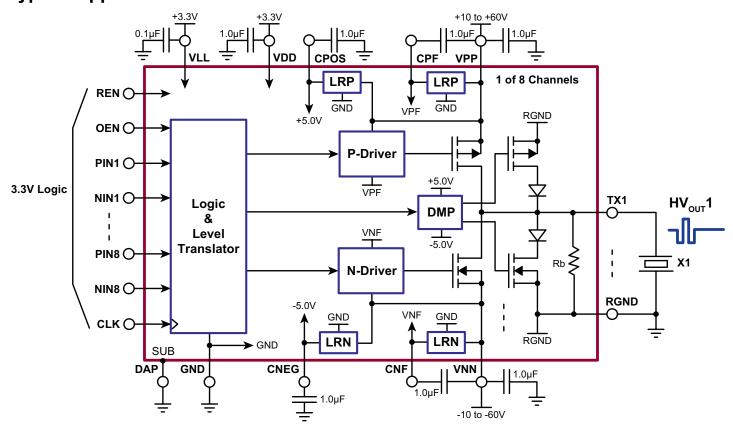

The Supertex HV7350 is an eight channel monolithic high voltage highspeed pulse generator with built-in fast return to zero damping FETs. This high voltage and high-speed integrated circuit is designed for portable medical ultrasound image devices.

HV7350 consists of a controller logic interface circuit, level translators, MOSFET gate drives, and high current power P-channel and N-channel MOSFETs as the output stage for each channel.

The output peak currents of each channel are guaranteed to be over  $\pm 1.0 A$  with up to  $\pm 60 V$  pulse swings as well as return-to-zero (RTZ) mode. The gate drivers for the output MOSFETs are powered by built-in linear 5.0V regulators referenced to  $V_{PP}$  and  $V_{NN}$ . This direct coupling topology of the gate drivers not only saves four floating voltage supplies or AC coupling capacitors per channel, but also makes the PCB layout smaller and easier.

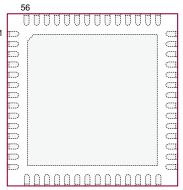

An input clock pin is available to realign all the logic input control lines to a master clock. Precise logic timing is always essential in any ultrasound systems.

### **Typical Application Circuit**

### **Ordering Information**

| Part Number     | Package           | Packing   |

|-----------------|-------------------|-----------|

| HV7350K6-G      | 56-Lead (8x8) QFN | 250/ Tray |

| HV7350K6-G M937 | 56-Lead (8x8) QFN | 2000/Reel |

### **Absolute Maximum Ratings**

| Parameter                                                                  | Value          |

|----------------------------------------------------------------------------|----------------|

| VSUB, substrate voltage is GND                                             | 0V             |

| V <sub>LL</sub> , Positive logic supply                                    | -0.5V to +5.5V |

| V <sub>DD</sub> , Positive logic and level translator supply               | -0.5V to +5.5V |

| C <sub>POS</sub> to GND, Positive level translator circuit                 | -0.5V to +5.5V |

| C <sub>NEG</sub> to GND, Negative level translator circuit                 | +0.5V to -5.5V |

| (V <sub>PP</sub> - C <sub>PF</sub> ), Positive gate driver circuit         | -0.5V to +5.5V |

| $(C_{NF} - V_{NN})$ , Negative gate driver circuit                         | -0.5V to +5.5V |

| $(V_{PP} - V_{NN})$ Differential high voltage supply                       | +130V          |

| V <sub>pp</sub> , High voltage positive supply                             | -0.5V to +65V  |

| V <sub>NN</sub> , High voltage negative supply                             | +0.5V to -65V  |

| All logic input PIN <sub>x</sub> , NIN <sub>x</sub> , OEN and REN voltages | -0.5V to +5.5V |

| Operating temperature                                                      | -40°C to 125°C |

| Storage temperature                                                        | -65°C to 150°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

### **Pin Configuration**

56-Lead QFN (top view)

### **Package Marking**

L = Lot Number YY = Year Sealed WW = Week Sealed A = Assembler ID C = Country of Origin . = "Green" Packaging

Package may or may not include the following marks: Si or

#### 56-Lead QFN

### **Typical Thermal Resistance**

| <i>7</i> I        |                         |

|-------------------|-------------------------|

| Package           | $oldsymbol{	heta_{ja}}$ |

| 56-Lead (8x8) QFN | 21°C/W                  |

# Output Current & R<sub>on</sub>

| I <sub>sc</sub> | $R_{onP}$ | R <sub>onN</sub> | I <sub>DMP</sub> | $R_{onDP}$ | $R_{\scriptscriptstyle{onDN}}$ |

|-----------------|-----------|------------------|------------------|------------|--------------------------------|

| 1.5A            | 13Ω       | 6.5Ω             | 1.5A             | 13Ω        | 00.8                           |

- $1.V_{PP}/V_{NN} = +/-60V, V_{DD} = +3.3V; REN = 1$ 2.  $I_{SC}$  is current into  $1.0\Omega$  to GND;

- 3.  $I_{DMP}$  is current from +/-30V connected to  $T_{x}$  pin.

- 4. Max pulse width for current measurement on  $T_x$  pin is 100ns.

### Power-Up Sequence

| Step | Description                                   |  |  |  |  |  |  |  |  |

|------|-----------------------------------------------|--|--|--|--|--|--|--|--|

| 1    | V <sub>LL</sub> with logic signal low         |  |  |  |  |  |  |  |  |

| 2    | $V_{DD}$                                      |  |  |  |  |  |  |  |  |

| 3    | REN = 1 (external supplies on)                |  |  |  |  |  |  |  |  |

| 4    | $V_{_{\mathrm{PP}}}$ and $V_{_{\mathrm{NN}}}$ |  |  |  |  |  |  |  |  |

| 5    | Logic control signals active                  |  |  |  |  |  |  |  |  |

### **Power-Down Sequence**

| Step | Description                     |

|------|---------------------------------|

| 1    | All logic signals go to low     |

| 2    | $V_{_{PP}}$ and $V_{_{NN}}$     |

| 3    | REN = 0 (external supplies off) |

| 4    | $V_{_{ m DD}}$                  |

| 5    | $V_{\text{LL}}$                 |

#### Note:

Powering up/down in any arbitrary sequence will not cause any damage to the device. The powering up/down sequence is only recommended in order to minimize possible inrush current.

### **Operating Supply Voltages and Current (Eight Active Channels)**

(Operating conditions, unless otherwise specified,  $V_{LL}$  = +3.3V,  $V_{DD}$  = +3.3V,  $V_{PP}$  = +60V,  $V_{NN}$  = -60V,  $V_{CLK}$  = +3.3V,  $V_{A}$  = 25°C)

| Sym                 | Parameter                      | Min  | Тур  | Max  | Units | Conditions                              |

|---------------------|--------------------------------|------|------|------|-------|-----------------------------------------|

| V <sub>DD</sub>     | V <sub>DD</sub> voltage supply | 2.97 | 3.30 | 5.20 | V     |                                         |

| UVLO <sub>DD</sub>  | V <sub>DD</sub> UVLO           | 2.30 | 2.60 | 2.80 | V     |                                         |

| V <sub>LL</sub>     | Logic voltage reference        | 2.50 | 3.30 | 5.00 | V     |                                         |

| UVLO <sub>LL</sub>  | V <sub>LL</sub> UVLO           | 1.30 | 1.55 | 1.70 | V     |                                         |

| V <sub>PP</sub>     | Positive high voltage supply   | +10  | -    | +60  | V     |                                         |

| V <sub>NN</sub>     | Negative high voltage supply   | -60  | -    | -10  | V     |                                         |

| I <sub>LLQ</sub>    | V <sub>LL</sub> current        | -    | 8.0  | -    |       |                                         |

| I <sub>DDQ</sub>    | V <sub>DD</sub> current        | -    | 1.0  | -    |       | OEN = REN = 0                           |

| I <sub>PPQ</sub>    | V <sub>PP</sub> current        | -    | 5.0  | 10   | μA    |                                         |

| I <sub>NNQ</sub>    | V <sub>NN</sub> current        | -    | 5.0  | 10   |       |                                         |

| I <sub>LLEN</sub>   | V <sub>LL</sub> current        | -    | 13   | 20   |       |                                         |

| I <sub>DDEN</sub>   | V <sub>DD</sub> current        | -    | 480  | 700  |       | OEN = REN = 1                           |

| I <sub>PPEN</sub>   | V <sub>PP</sub> current        | -    | 220  | 350  | μA    | 5.0ms after f = 0MHz                    |

| I <sub>NNEN</sub>   | V <sub>NN</sub> current        | -    | 300  | 400  |       |                                         |

| I <sub>DDCW</sub>   | V <sub>DD</sub> current        | -    | 2.3  | -    |       | f = 5.0MHz, Continuous, no loads,       |

| I <sub>PPCW</sub>   | V <sub>PP</sub> current        | -    | 80   | -    | mA    | for calculation reference only.         |

| I <sub>NNCW</sub>   | V <sub>NN</sub> current        | -    | 80   | -    |       |                                         |

| I <sub>LL,CLK</sub> | V <sub>LL</sub> current        | -    | 33   | -    | μA    | f <sub>CLK</sub> = 10MHz, PIN = NIN = 0 |

### **Electrical Characteristics**

(Operating conditions, unless otherwise specified,  $V_{LL}$  = +3.3V,  $V_{DD}$  = +3.3V,  $V_{PP}$  = +60V,  $V_{NN}$  = -60V,  $V_{CLK}$  = +3.3V,  $V_{A}$  = 25°C)

#### **Pulser P-Channel MOSFET**

| Sym              | Parameter                 | Min | Тур  | Max | Units | Conditions              |

|------------------|---------------------------|-----|------|-----|-------|-------------------------|

| I <sub>OUT</sub> | Output saturation current | 1.0 | 1.5  | -   | Α     |                         |

| R <sub>on</sub>  | Channel resistance        | -   | 13.2 | -   | Ω     | I <sub>SD</sub> = 100mA |

### **Pulser N-Channel MOSFET**

| Sym              | Parameter                 | Min | Тур | Max | Units | Conditions              |

|------------------|---------------------------|-----|-----|-----|-------|-------------------------|

| I <sub>OUT</sub> | Output saturation current | 1.0 | 1.5 | -   | Α     |                         |

| R <sub>on</sub>  | Channel resistance        | -   | 8.0 | -   | Ω     | I <sub>SD</sub> = 100mA |

**Damping P-Channel MOSFET**

| Sym              | Parameter                 | Min | Тур | Max | Units | Conditions              |

|------------------|---------------------------|-----|-----|-----|-------|-------------------------|

| I <sub>OUT</sub> | Output saturation current | 1.0 | 1.5 | -   | Α     |                         |

| R <sub>on</sub>  | Channel resistance        | -   | 13  | -   | Ω     | I <sub>SD</sub> = 100mA |

**Damping N-Channel MOSFET**

| Sym              | Parameter                 | Min | Тур | Max | Units | Conditions              |

|------------------|---------------------------|-----|-----|-----|-------|-------------------------|

| I <sub>OUT</sub> | Output saturation current | 1.0 | 1.5 | -   | Α     |                         |

| R <sub>on</sub>  | Channel resistance        | -   | 9.0 | -   | Ω     | I <sub>SD</sub> = 100mA |

**Logic Inputs**

| Sym                  | Parameter                | Min                   | Тур | Max                   | Units | Conditions                              |

|----------------------|--------------------------|-----------------------|-----|-----------------------|-------|-----------------------------------------|

| V <sub>IH</sub>      | Input logic high voltage | 0.7 • V <sub>LL</sub> | -   | V <sub>LL</sub>       | V     | V = 2.5 to 2.2V                         |

| V <sub>IL</sub>      | Input logic low voltage  | 0                     | -   | 0.3 • V <sub>LL</sub> | V     | $V_{LL} = 2.5 \text{ to } 3.3 \text{V}$ |

| $V_{_{\mathrm{IH}}}$ | Input logic high voltage | 0.8 • V <sub>LL</sub> | -   | V <sub>LL</sub>       | V     | \/ = 5 0\/                              |

| V <sub>IL</sub>      | Input logic low voltage  | 0                     | -   | 0.2 • V <sub>LL</sub> | V     | V <sub>LL</sub> = 5.0V                  |

| I <sub>IH</sub>      | Input logic high current | -                     | -   | 10                    | μA    |                                         |

| I <sub>IL</sub>      | Input logic low current  | -10                   | -   | -                     | μA    |                                         |

| C <sub>IN</sub>      | Input logic capacitance  | -                     | -   | 5.0                   | pF    |                                         |

### **MOSFET Drain Bleed Resistor**

| Sym                | Parameter                   | Min | Тур | Max | Units | Conditions |

|--------------------|-----------------------------|-----|-----|-----|-------|------------|

| R <sub>B1~8</sub>  | Output Bleed Resistance     | 12  | 17  | 25  | kΩ    |            |

| P <sub>RB1~8</sub> | Bleed Resistors Power Limit | -   | -   | 50  | mW    |            |

AC Electrical Characteristics (Operating conditions, unless otherwise specified,  $V_{LL}$  = +3.3V,  $V_{DD}$  = +3.3V,  $V_{PP}$  = +60V ,  $V_{NN}$  = -60V,  $V_{CLK}$  = +3.3V,  $V_{A}$  = 25°C)

| Sym                       | Parameter                            | Min | Тур  | Max | Units | Conditions                                                                                                                       |  |  |

|---------------------------|--------------------------------------|-----|------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| t <sub>r</sub>            | Output rise time                     | -   | 30   | -   | ns    | 330pF//2.5kΩ load                                                                                                                |  |  |

| t <sub>f</sub>            | Output fall time                     | -   | 30   | -   | ns    | 10 - 90%                                                                                                                         |  |  |

| t <sub>EN</sub>           | Enable time                          | -   | 300  | 500 | μs    | Cap value see page 1 diagram.                                                                                                    |  |  |

| t <sub>DIS</sub>          | Disable time                         | -   | 2.8  | 10  | μs    | OEN = REN                                                                                                                        |  |  |

| t <sub>d1</sub>           | Delay time on PIN <sub>x</sub> rise  | -   | 12   | -   |       |                                                                                                                                  |  |  |

| t <sub>d2</sub>           | Delay time on NIN <sub>x</sub> rise  | -   | 12   | -   |       | 1.0Ω resistor load, D%<1% (See timing diagram) 50% inputs to 50% T <sub>x</sub> current                                          |  |  |

| t <sub>d3</sub>           | Delay time on damping rise           | -   | 12   | -   | ns    |                                                                                                                                  |  |  |

| t <sub>d4</sub>           | Delay time on damping fall           | -   | 12   | -   |       |                                                                                                                                  |  |  |

| t <sub>dc</sub>           | Delay time on CLK rise               | -   | 9.0  | -   |       |                                                                                                                                  |  |  |

| $\Delta t_{\text{DELAY}}$ | Delay time matching                  | -   | ±3.0 | -   | ns    | P to N, channel to channel                                                                                                       |  |  |

| t <sub>j</sub>            | Delay jitter on rise or fall         | -   | TBD  | -   | ps    | $V_{pp}/V_{NN}$ = +/-25V, input tr 50% to HV <sub>OUT</sub> t <sub>r</sub> or t <sub>r</sub> 50%, with 330pF//2.5k $\Omega$ load |  |  |

| t <sub>rr</sub>           | RTZ FETs drain diode t <sub>rr</sub> | -   | 25   | -   | ns    | $I_F = 1.0A, I_R = 1.0A, R_L = 10\Omega$                                                                                         |  |  |

| f <sub>CLK</sub>          | Re-timing clock frequency            | 10  | 220  | -   | MHz   |                                                                                                                                  |  |  |

| $t_{RC}, t_{FC}$          | Re-timing clock rise & fall times    | -   | 0.5  | 5.0 | ns    |                                                                                                                                  |  |  |

| t <sub>su</sub>           | Set-up time, PIN/NIN to CLK          | 2.0 | -    | -   | ns    |                                                                                                                                  |  |  |

| t <sub>H</sub>            | Hold time, CLK to PIN/NIN            | 1.0 | -    | -   | ns    |                                                                                                                                  |  |  |

| t <sub>CLK_LO</sub>       | Clock time low                       | 2.0 | -    | 100 | ns    | CLK input must have at least one                                                                                                 |  |  |

| t <sub>CLK_HI</sub>       | Clock time high                      | 2.0 | -    | 100 | ns    | pulse before PIN and NIN inputs are                                                                                              |  |  |

| t <sub>CLK_REC</sub>      | Clock recognition time               | -   | 2.0  | -   | ns    | not zero. Be sure to return inputs to                                                                                            |  |  |

| t <sub>CLK_RLS</sub>      | Clock release time                   | 150 | 300  | 800 | ns    | zero before stopping clock.                                                                                                      |  |  |

| f <sub>out</sub>          | Output frequency range               | -   | -    | 20  | MHz   | 100Ω resistor load                                                                                                               |  |  |

| HD2                       | Second harmonic distortion           | -   | -40  | -   | dB    | 1002 Tesistor load                                                                                                               |  |  |

| C <sub>oss</sub>          | Output capacitance                   | -   | 50   | -   | pF    | $V_{DS}$ = 25V, f = 1.0MHz , of $T_X$ pin total                                                                                  |  |  |

### **Truth Table**

|     | Logic    | Inputs           |                  | TX <sub>n</sub> Output |         |      |                                            |  |  |  |

|-----|----------|------------------|------------------|------------------------|---------|------|--------------------------------------------|--|--|--|

| OEN | CLK      | PIN <sub>x</sub> | NIN <sub>x</sub> | VPP                    | VNN     | RGND | Note                                       |  |  |  |

| 1   | VLL      | 0                | 0                | OFF                    | OFF     | ON   |                                            |  |  |  |

| 1   | VLL      | 1                | 0                | ON                     | OFF     | OFF  | Asynchronous Mode                          |  |  |  |

| 1   | VLL      | 0                | 1                | OFF                    | ON      | OFF  | Output change on PIN/NIN                   |  |  |  |

| 1   | VLL      | 1                | 1                | OFF                    | OFF OFF |      |                                            |  |  |  |

| 1   | <u>_</u> | 0                | 0                | OFF                    | OFF     | ON   | Synahranaua Mada                           |  |  |  |

| 1   | <u>_</u> | 1                | 0                | ON                     | OFF     | OFF  | Synchronous Mode Output change at retiming |  |  |  |

| 1   | <u>_</u> | 0                | 1                | OFF                    | ON      | OFF  | clock(CLK) rising edge,                    |  |  |  |

| 1   | <u>_</u> | 1                | 1                | OFF                    | OFF     | OFF  | registered by PIN/NIN                      |  |  |  |

| 0   | Х        | Х                | Х                | OFF                    | OFF     | OFF  | Disabled                                   |  |  |  |

### **Switching Time Diagram**

## **Pin Description**

|     | Cription |                                                                                                                                                                                           |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin | Name     | Description                                                                                                                                                                               |

| 1   | PIN2     | Input logic control of high voltage output P-FET for channel 2, Hi = on, Low = off. (see logic table)                                                                                     |

| 2   | NIN2     | Input logic control of high voltage output N-FET for channel 2, Hi = on, Low = off. (see logic table)                                                                                     |

| 3   | PIN3     | Input logic control of high voltage output P-FET for channel 3, Hi = on, Low = off. (see logic table)                                                                                     |

| 4   | NIN3     | Input logic control of high voltage output N-FET for channel 3, Hi = on, Low = off. (see logic table)                                                                                     |

| 5   | PIN4     | Input logic control of high voltage output P-FET for channel 4, Hi = on, Low = off. (see logic table)                                                                                     |

| 6   | NIN4     | Input logic control of high voltage output N-FET for channel 4, Hi = on, Low = off. (see logic table)                                                                                     |

| 7   | OEN      | Output enable Hi = on, Low = off. See logic truth table                                                                                                                                   |

| 8   | REN      | Built-in positive and negative 5V voltage regulators enable. Hi = on, Low = off. If REN = 0, external floating 5V power supplies may be supplied across CPF, CNF CPOS and CNEG capacitors |

| 9   | PIN5     | Input logic control of high voltage output P-FET for channel 5, Hi = on, Low = off. (see logic table)                                                                                     |

| 10  | NIN5     | Input logic control of high voltage output N-FET for channel 5, Hi = on, Low = off. (see logic table)                                                                                     |

| 11  | PIN6     | Input logic control of high voltage output P-FET for channel 6, Hi = on, Low = off. (see logic table)                                                                                     |

| 12  | NIN6     | Input logic control of high voltage output N-FET for channel 6, Hi = on, Low = off. (see logic table)                                                                                     |

| 13  | PIN7     | Input logic control of high voltage output P-FET for channel 7, Hi = on, Low = off. (see logic table)                                                                                     |

| 14  | NIN7     | Input logic control of high voltage output N-FET for channel 7, Hi = on, Low = off. (see logic table)                                                                                     |

| 15  | PIN8     | Input logic control of high voltage output P-FET for channel 8, Hi = on, Low = off. (see logic table)                                                                                     |

| 16  | NIN8     | Input logic control of high voltage output N-FET for channel 8, Hi = on, Low = off. (see logic table)                                                                                     |

| 17  | VLL      | Logic supply voltage and reference input (+3.3V)                                                                                                                                          |

| 18  | GND      | Logic and circuit return ground (0V)                                                                                                                                                      |

| 19  | VDD      | Positive voltage power supply (+3.3V)                                                                                                                                                     |

| 20  | VPP      |                                                                                                                                                                                           |

| 21  | VPP      | Positive high voltage power supply (+10 to +60V)                                                                                                                                          |

| 22  | VPP      |                                                                                                                                                                                           |

| 23  | CPF      | Built-in linear voltage VPF regulator output decoupling capacitor pin, 1uF from VPP to CPF per each                                                                                       |

| 24  | CNF      | Built-in linear voltage VNF regulator output decoupling capacitor pin, 1uF from CNF to VNN per each                                                                                       |

| 25  | VNN      |                                                                                                                                                                                           |

| 26  | VNN      | Negative high voltage power supply (-10 to -60V)                                                                                                                                          |

| 27  | VNN      |                                                                                                                                                                                           |

| 28  | TX8      | T <sub>x</sub> pulser channel 8 output                                                                                                                                                    |

| 29  | RGND     | Damping ground and bleed resistors common return ground                                                                                                                                   |

| 30  | TX7      | T <sub>x</sub> pulser channel 7 output                                                                                                                                                    |

| 31  | RGND     | Damping ground and bleed resistors common return ground                                                                                                                                   |

| 32  | TX6      | T <sub>x</sub> pulser channel 6 output                                                                                                                                                    |

### Pin Description (cont.)

| Pin       | Name      | Description                                                                                                                               |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0.0       |           |                                                                                                                                           |

| 33        | RGND      | Damping ground and bleed resistors common return ground                                                                                   |

| 34        | TX5       | T <sub>x</sub> pulser channel 5 output                                                                                                    |

| 35        | CNEG      | Built-in linear voltage -5V regulator output decoupling capacitor pin, 1.0uF from CNEG to GND                                             |

| 36        | CPOS      | Built-in linear voltage +5V regulator output decoupling capacitor pin, 1.0uF from CPOS to GND                                             |

| 37        | TX4       | T <sub>x</sub> pulser channel 4 output                                                                                                    |

| 38        | RGND      | Damping ground and bleed resistors common return ground                                                                                   |

| 39        | TX3       | T <sub>x</sub> pulser channel 3 output                                                                                                    |

| 40        | RGND      | Damping ground and bleed resistors common return ground                                                                                   |

| 41        | TX2       | T <sub>x</sub> pulser channel 2 output                                                                                                    |

| 42        | RGND      | Damping ground and bleed resistors common return ground                                                                                   |

| 43        | TX1       | T <sub>x</sub> pulser channel 1 output                                                                                                    |

| 44        | VNN       |                                                                                                                                           |

| 45        | VNN       | Negative high voltage power supply (-10 to -60V)                                                                                          |

| 46        | VNN       |                                                                                                                                           |

| 47        | CNF       | Built-in linear voltage VNF regulator output decoupling capacitor pin, 1uF from CNF to VNN per each                                       |

| 48        | CPF       | Built-in linear voltage VPF regulator output decoupling capacitor pin, 1uF from VPP to CPF per each                                       |

| 49        | VPP       |                                                                                                                                           |

| 50        | VPP       | Positive high voltage power supply (+10 to +60V)                                                                                          |

| 51        | VPP       |                                                                                                                                           |

| 52        | VDD       | Positive voltage power supply (+3.3V)                                                                                                     |

| 53        | GND       | Logic and circuit return ground (0V)                                                                                                      |

| 54        | CLK       | Re-timing register clock input. Connect to V <sub>LL</sub> to disable the re-timing function                                              |

| 55        | PIN1      | Input logic control of high voltage output P-FET for channel 1, Hi = on, Low = off. (see logic table)                                     |

| 56        | NIN1      | Input logic control of high voltage output N-FET for channel 1, Hi = on, Low = off. (see logic table)                                     |

| VSUB (The | rmal Pad) | Substrate bottom is internally connected to the central thermal pad on the bottom of package. It must be connected to GND (0V) externally |

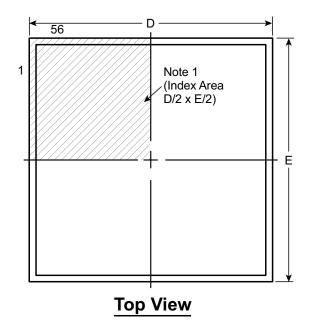

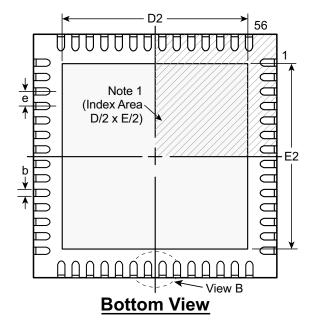

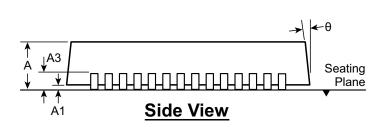

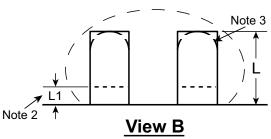

### 56-Lead QFN Package Outline (K6)

### 8.00x8.00mm body, 1.00mm height (max), 0.50mm pitch

#### Notes:

- A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symbol         |     | Α    | A1   | А3          | b    | D     | D2                | E     | E2                | е           | L    | L1   | θ          |

|----------------|-----|------|------|-------------|------|-------|-------------------|-------|-------------------|-------------|------|------|------------|

| Dimension (mm) | MIN | 0.80 | 0.00 | 0.20<br>REF | 0.18 | 7.85* | 2.75              | 7.85* | 2.75              | 0.50<br>BSC | 0.30 | 0.00 | <b>0</b> ° |

|                | NOM | 0.90 | 0.02 |             | 0.25 | 8.00  | 5.70              | 8.00  | 5.70              |             | 0.40 | -    | -          |

|                | MAX | 1.00 | 0.05 |             | 0.30 | 8.15* | 6.70 <sup>†</sup> | 8.15* | 6.70 <sup>†</sup> | ВОО         | 0.50 | 0.15 | 14°        |

JEDEC Registration MO-220, Variation VLLD-2, Issue K, June 2006.

Drawings are not to scale.

Supertex Doc.#: DSPD-56QFNK68X8P050, Version A031010.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.